Introduction

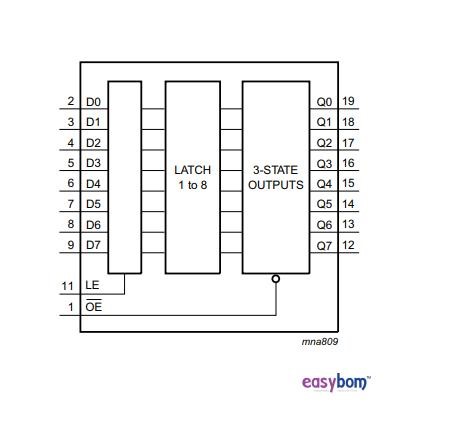

The 74HC573D,652 is an 8-bit transparent D-type latch with a 3-state that has three-state outputs. It has both output and latch enable options. If LE is high, all input data is inserted into the latches. In this case, the latches remain transparent and the output of a latch will alter each time the D-input change. If LE is low, the latches will store the data that was available at the time of setting up prior to the HIGH-to-LOW transition LE. A HIGH state on OE causes the outputs to assume a high-impedance ON-state. The operation from the OE input is not a factor in the status that the latches are in. Inputs have clamp diodes. This allows the use of current-limiting resistors to connect inputs to levels that exceed VCC.

You Should Read More About: Packaging Ideas For Small Items

Features

A wide range of supply voltages from 2.0 up to 6.0 V

Low power dissipation CMOS

High noise resistance

Outputs and inputs are in opposite directions of the package making it possible to interact with microprocessors

It is a useful port for input and output to microprocessors as well as microcomputers.

3state non-inverting outputs that are not inverting for bus-oriented applications.

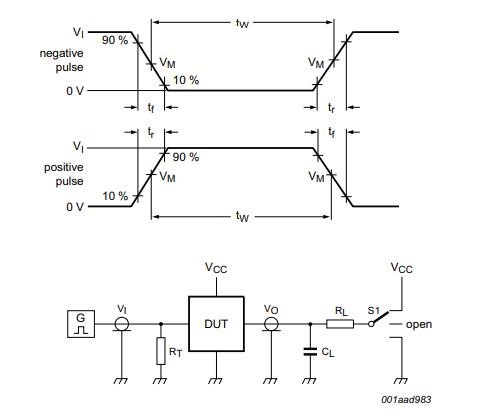

Diagram

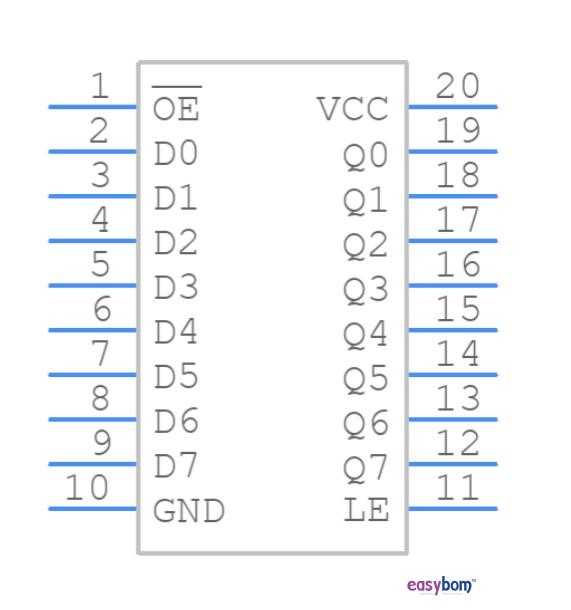

CAD Model

CAD Model

Symbol

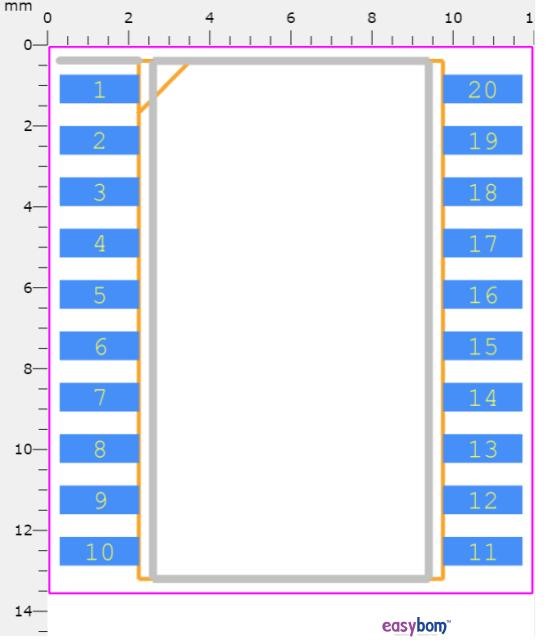

PCB Footprints

3D Models

Specifications

Supply Chain

Factory Lead Time – 4 Weeks

Physical

Package / Case – 20-SOIC (0.295, 7.50mm Width)

Number of Pins – 20

Technical

Operating Temperature – -40°C~125°C

Circuits of 74HC573D,652

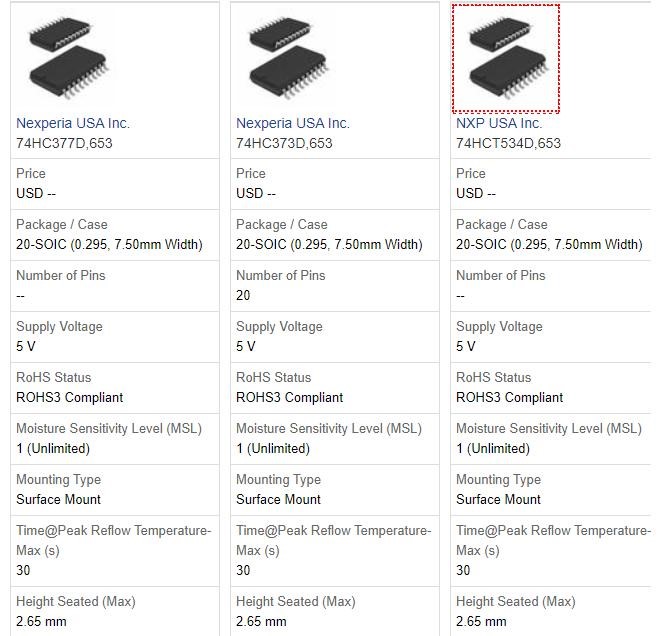

Alternative Models

74HC377D,653

74HC373D,653

74HCT534D,653

Where to Use 74HC573D,652?

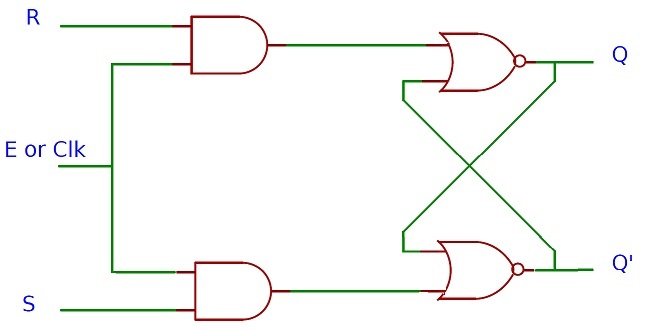

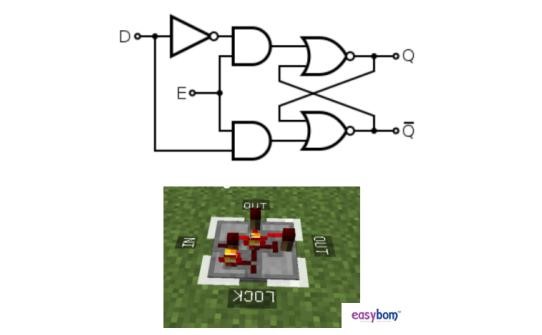

What is a Latch: Latch Definition & Meaning

The 74HC573D,652 latch is a form of memory cell circuit that is sensitive to pulse levels. It can alter its state at an input level that is specific to the pulse. It refers to the ability to temporarily store an input signal in order to preserve an exact level of the state. The primary purpose of latches is to cache. It can control the speed of its out-of-sync peripherals. It is also able to it is able to solve the driver issue and resolve the I/O ports to be used for input and output. Its output state doesn’t alter with the state of the input. It preserves the state of the input to the output after a signal is received. It will not alter its output up until the following latch signal is received. Latches are commonly employed within integrated circuits. They serve to store data in the timing circuit in digital circuits. Sometimes, they are used to store data in mathematical circuits.

The Distinction between Buffers and Latches:

The purpose of the latch is to secure the current state of the circuit. It ensures that the data transmitted to the CPU on the output portion in the interconnect circuit over a certain period of time of locking state does not change until the lock is released. It stores the current state. It makes the data sent by the CPU in the output end of the interface circuit after a period of locking state no longer change until unlocked.

The buffer register can also be referred to as the buffer. It contains two kinds of output buffer and an input buffer. The first one is used to store temporary information sent by peripherals so that the processor is able to retrieve it later. It is also used to store data temporarily that the processor sends to peripherals. With the CNC buffer, it’s possible to monitor and buffer the high-speed CPU and the slower peripherals. It is synchronized with the transmission of data.

How to Use 74HC573D,652?

The 74HC573D,652 latches are a great way to help to reduce the stress upon the processor. Once the processor has transferred information to the latch, and stores it the output pin of the latch stores data’s state until the next time the information is registered. This frees the processor’s processing time as well as IO pins until display information in the nixie tube remains not changed. Processing time for the processor will be restricted to the time that the display content changes. It is a small portion of the total display time. The processor will have the time to do other tasks. It also saves MCU time.

Parts with Similar Specs

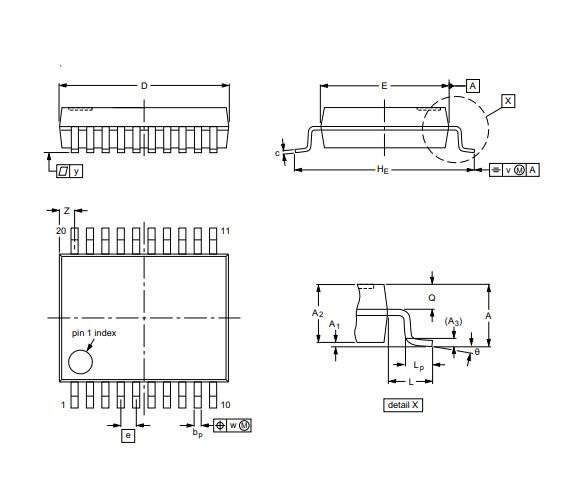

Package Dimensions

About the Manufacturer

Nexperia is dedicated to Discretes, Logic, and MOSFETs devices. This new company became independent at the beginning of 2017.

Datasheet

Popular by region and Trend Analysis

More detail please visit 74HC573D,652

Conclusion

The 74HC573D,652 latch is also available as a separate item and used in a different way. Its delay in data validity is more efficient as compared to the clock signal. This implies that the data signal is generated first, while the data signal follows. In certain situations use of an external latch is required to be connected to the port for I/O on the MCU. For instance when the microcontroller is connected to an external memory that is coupled with the latch. This is to allow address reuse. Imagine there are 8 pins on the MCU port that can be used for data and address signals. Then, you can employ the latch to block the address before locking.

From easybom.com